# A Cooperation Agreement for 10 Gigabit Ethernet Transceiver Package

Issue 3.0

18th September 2002

#### 1 Revision

| Rev | Date                           | Ву             | Purpose/Changes                                                                                                                                                                                                                                          |

|-----|--------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | 1 May 2001                     | Antony Spilman | First Public Issue                                                                                                                                                                                                                                       |

| 2.0 | 26 September 2001              | Antony Spilman | Finalize: mechanical dimensions, key functionality, electrical pin-outs, optical Interfaces                                                                                                                                                              |

| 2.1 | 15 <sup>th</sup> February 2002 | Antony Spilman | Legal section split. Dimensional changes to Bezel. PCB thickness range reduced Adaptable power supply improved. Updates to XENPAK OUI. Updates to LASI. Updates to NVR control register. Reserved areas in NVR for intelligent power up and diagnostics. |

| 3.0 | 18th September 2002            | Antony Spilman | See below                                                                                                                                                                                                                                                |

#### Rev 3.0 Main changes

#### **Feature Additions**

- Major updates to Section 11 adding XENPAK Digital Optical monitoring functions

- Added Optional Low power startup to Section 10.4.2.

#### Mechanical Changes/Corrections

Corrected JJ2 to 7 mm (TT2 with tolerance was causing interference with side flange of bezel)

#### **Electrical Clarifications/Corrections**

- Change fixed Power Steady State Voltage Accuracy to +/- 5% from +/- 3% Table 7, LASI is still +/- 3%.

- Changed minimum APS current limit to 100 mA from 400 mA.

- Corrected APS fault condition in Section 10.3

- Changed wording of paragraph 2 of 10.4 related to ramp up time of fixed PSUs.

- Added footnote to Fig 13. saying it gives an example of one termination method and the pin definition table should be read for detail.

- Clarified reset states and state transitions and initialization after reset in section 10.5.3.

- Updated references to 802.3ae in the OUI section 10.8.2

- Added 3<sup>rd</sup> paragraph to section 10.8.3 saying that NVR only uses least 8 significant bits of MDIO register for data.

- Fixed NVR control bit latching issue and added general clarification to section 10.9. State diagram and notes have been substantially updated.

- LASI section 10.13 has been substantially clarified and updated

- Created a new "optional capability" register at NVR location 32891, see 10.12.21.

Flagged LPS ability in bit 0 of this register.

# 2 Summary of MSA Group Members

| Company                | Representative       | Contact info                     |

|------------------------|----------------------|----------------------------------|

| Agere Systems          | Michael Peppler      | peppler@agere.com                |

| Agilent Technologies   | Antony Spilman       | antony_spilman@agilent.com       |

| Blaze Network Products | Todd Whitaker        | twhitaker@blazenp.com            |

| ExceLight              | Gregg Cockroft       | gcockroft@excelight.com          |

| E20                    | Mike Hartmann        | mjhartmann@e2oinc.com            |

| Finisar                | Christian Urricariet | curricariet@finisar.com          |

| Hitachi Cable          | Louis Marra          | Imarra@hitachi-cable.com         |

| Ignis Optics           | Steve Joiner         | steve.joiner@ignis-optics.com    |

|                        | Chris Simoneaux      | chris.simoneaux@ignisoptics.com  |

| Infineon Technologies  | Rami Kanama          | rami.kanama@infineon.com         |

| JDS Uniphase           | Ladd Freitag         | laddf@us.ibm.com                 |

|                        | Jerry Wood           | Jerry.Wood@us.jdsuniphase.com    |

| Intel                  | Peter Francis        | peter.francis@intel.com          |

| Luminent               | Ed Pollock           | epollock@luminentinc.com         |

| Mitsubishi Electric    | Matthew Nicholson    | matthew.nicholson@hq.melco.co.jp |

| Molex                  | John Dallesasse      | jdallesasse@molex.com            |

| Multiplex              | David Chen           | cdchen@multiplexinc.com          |

| NEC                    | Tetsuyuki Suzaki     | tet-suzaki@cj.jp.nec.com         |

| Network Elements       | Raj Savara           | Rsavara@networkelements.com      |

| Nortel Networks        | Richard Jokiel       | jokiel@nortelnetworks.com        |

| OpNext                 | Atsushi Takai        | atsushi.takai@opnext.com         |

|                        | Ed Cornejo           | Ecornejo@opnext.com              |

| Optillion              | Bertil Kronlund      | bertil.kronlund@optillion.com    |

| Picolight              | Tracy Earles,        | tracy.earles@picolight.com       |

|                        | David Kabal          | david.kabal@picolight.com        |

| Pine Photonics         | Alex Leibovich       | aleibovich@pinephotonics.com     |

| Stratos Lightwave      | Steve Tebo           | stebo@stratoslightwave.com       |

| Tyco Electronics       | Tom Riha             | rihat@tycoelectronics.com        |

| Vitesse                | Geeta George         | george@versonet.com              |

# 3 Summary of MSA Group Sponsors

| Company           | Representative  | Contact info                  |

|-------------------|-----------------|-------------------------------|

| Extreme Networks: | Andy Moorwood,  | amoorwood@extremenetworks.com |

| Nortel Networks:  | Richard Jokiel, | jokiel@nortelnetworks.com     |

# 4 Table of contents:

| 1  | REVISION                      | 2    |

|----|-------------------------------|------|

| 2  | SUMMARY OF MSA GROUP MEMBERS  | 3    |

| 3  | SUMMARY OF MSA GROUP SPONSORS | 3    |

| 4  | TABLE OF CONTENTS:            | 4    |

| 5  | LIST OF FIGURES               | 5    |

| 6  | LIST OF TABLES                | 6    |

| 7  | PURPOSE OF THE MSA            | 7    |

| 8  | MSA MECHANICAL                | 8    |

| 9  | XENPAK THERMAL REQUIREMENTS   | 20   |

| 10 | XENPAK ELECTRICAL INTERFACE   | . 21 |

| 11 | XENPAK DIAGNOSTICS            | 61   |

| 12 | APPENDIX 1A                   | 72   |

# 5 List of Figures

| Fig 1.  | Isometric Drawings                                                         | 8  |

|---------|----------------------------------------------------------------------------|----|

| Fig 2.  | DATUM Legend figure updated                                                | 9  |

| Fig 3.  | ORIENTATION KEYING OF TX AND RX ORIENTATION Vs PCB                         | 9  |

| Fig 4.  | Package Outline                                                            | 10 |

| Fig 5.  | Front Panel Opening and Host PCB                                           | 13 |

| Fig 6.  | Transceiver Printed Circuit Board Connector                                | 16 |

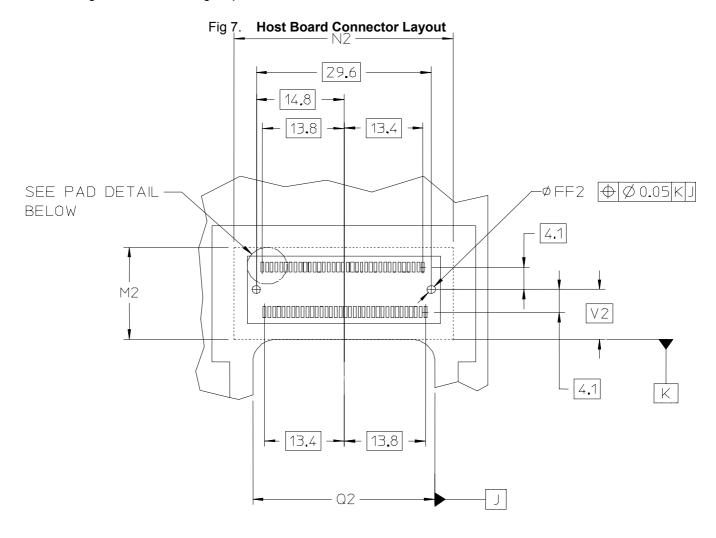

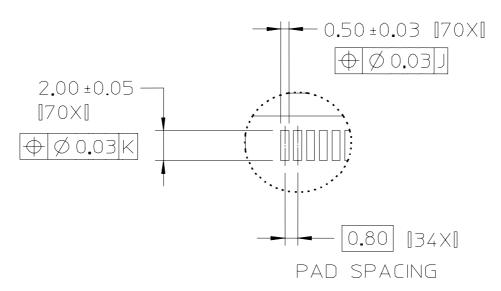

| Fig 7.  | Host Board Connector Layout                                                | 17 |

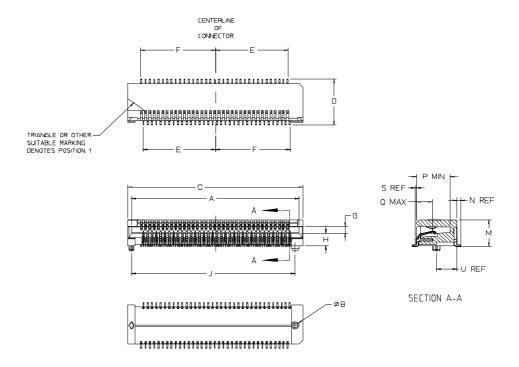

| Fig 8.  | Connector Drawing                                                          | 18 |

| Fig 9.  | Adaptable Power Supply                                                     | 22 |

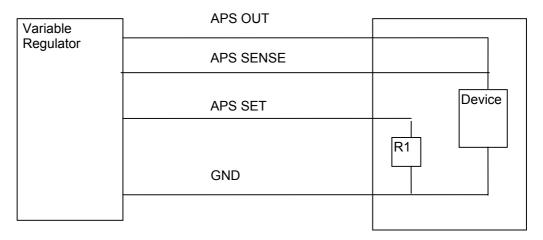

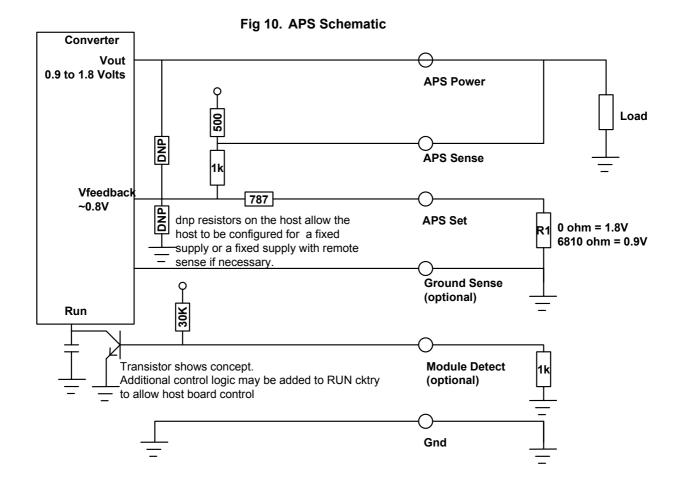

| Fig 10. | APS Schematic                                                              | 24 |

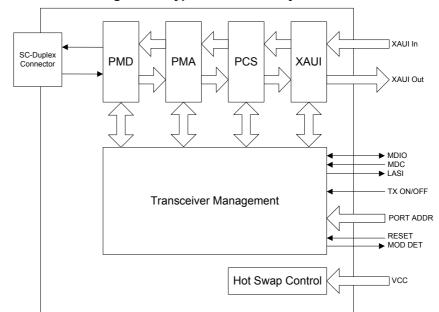

| Fig 11. | Functional Diagram of Typical XENPAK Style Transceiver                     | 27 |

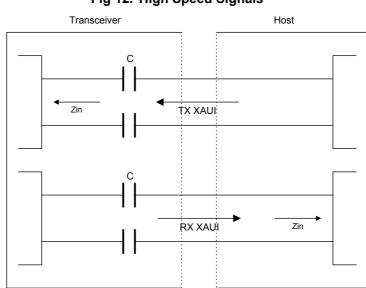

| Fig 12. | High Speed Signals                                                         | 27 |

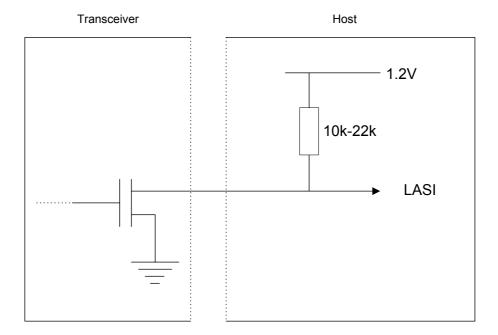

| Fig 13. | Example of Low Speed Output Configuration                                  | 28 |

| Fig 14. | Initialisation and Hot Swap Timing Diagram                                 | 29 |

| Fig 15. | Tx Off to Optical Output timing, normal operation                          | 30 |

| Fig 16. | Tx Off to Optical Output timing. See "Low Power Start-up", Section 10.4.2  | 30 |

| Fig 17. | XENPAK Transceiver Electrical Pad Layout                                   | 34 |

| Fig 18. | 10Gb Host Board Pad Layout and Names                                       | 35 |

| Fig 19. | Transceiver Identification after Hot Plugging                              | 36 |

| Fig 20. | NVR Access state diagram                                                   | 47 |

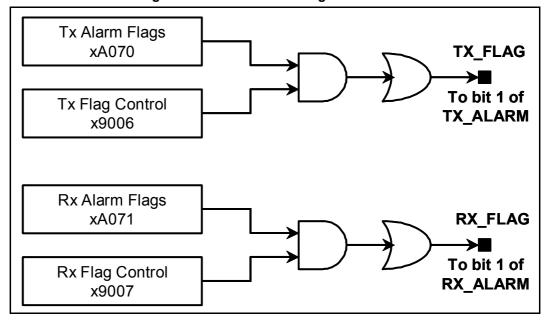

| Fig 21. | LASI Block Diagram                                                         | 56 |

| Fig 22. | XENPAK Digital Optical Monitoring MDIO Register Space                      | 61 |

| Fig 23. | DOM/LASI Block Diagram                                                     | 70 |

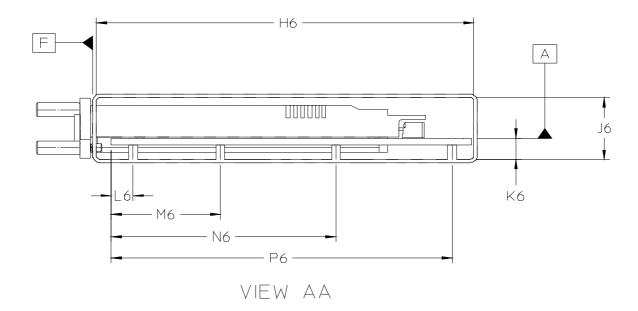

| Fig 24. | Cross Section of Test Fixture                                              | 73 |

| Fig 25. | Plan and Side view of Test Fixture                                         | 74 |

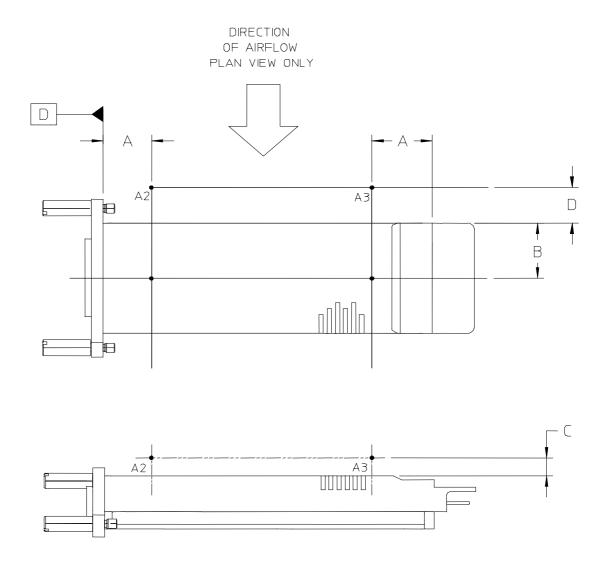

| Fig 26. | Optional air flow measurement points                                       | 75 |

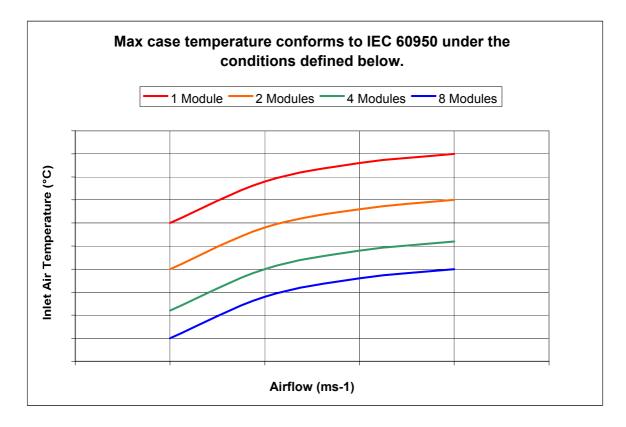

| Fia 27  | Case temperature vs. Inlet air temperature and, airflow at reference point | 77 |

# 6 List of Tables

| Table 1  | Package Dimensions                                                   | 12 |

|----------|----------------------------------------------------------------------|----|

| Table 2  | Front Panel Opening and Host PCB Dimensions                          | 15 |

| Table 3  | Connector Dimensions                                                 | 18 |

| Table 4  | Resistor Values for APS operation.                                   | 23 |

| Table 5  | Recommended Tolerances (+/-)                                         | 23 |

| Table 6  | APS Tolerances (+/-)                                                 | 24 |

| Table 7  | Fixed Power Rail Tolerances (+/-)                                    | 25 |

| Table 8  | Power on Reset characteristics                                       | 25 |

| Table 9  | Electrical Characteristics of Low Speed Interface                    | 28 |

| Table 10 | Relationship between the TRANSCEIVER RESET pin and MDIO Reset Bit    | 29 |

| Table 11 | Pin Function Definitions (Lower Row)                                 | 32 |

| Table 12 | Pin Function Definitions (Upper Row)                                 | 33 |

| Table 13 | XENPAK Register Set Overview                                         | 38 |

| Table 14 | NVR Register Map                                                     | 40 |

| Table 15 | NVR Control/Status Register (0x8000)                                 | 45 |

| Table 16 | RX_ALARM Status Register (0x9003)                                    | 57 |

| Table 17 | RX_ALARM Control Register (0x9000)                                   | 57 |

| Table 18 | TX_ALARM Status Register (0x9004)                                    | 58 |

| Table 19 | TX_ALARM Control Register (0x9001)                                   | 58 |

| Table 20 | Link Status Input Signals                                            | 59 |

| Table 21 | LASI Status Register (0x9005)                                        | 59 |

| Table 22 | LASI Control Register (0x9002)                                       | 60 |

| Table 23 | Temperature Value                                                    | 62 |

| Table 24 | Current Value (LSB = 2 uA)                                           | 62 |

| Table 25 | Tx Power Value                                                       | 62 |

| Table 26 | Rx Power Value                                                       | 63 |

| Table 27 | Alarm and Warning Threshold Memory Map                               | 63 |

| Table 28 | Table 6. Monitored A/D Value Memory Map                              | 65 |

| Table 29 | 807A: Digital Optical Monitoring (DOM) Capability                    | 66 |

| Table 30 | A06E (110): Optional Status Bits                                     | 66 |

| Table 31 | A06F (111): Digital Optical Monitoring (DOM) Capability - Extended   | 66 |

| Table 32 | A100 (256): Optional Digital Optical Monitoring (DOM) Control/Status | 67 |

| Table 33 | Alarm and Warning Flag Memory Map                                    | 68 |

| Table 34 | xA070 (112): TX_FLAG Status Bits                                     | 70 |

| Table 35 | x9006: TX_FLAG Control Bits                                          | 71 |

| Table 36 | xA071 (113): RX_FLAG Status Bits                                     | 71 |

| Table 37 | x9007: RX_FLAG Control Bits                                          | 71 |

| Table 38 | Test chamber conditions and test-points locations                    | 76 |

| Tahle 30 | Ontional Results for correlation                                     | 76 |

# 7 Purpose of the MSA

This MSA is bound by the operating guidelines published at:

http://www.xenpak.org/MSA/XENPAK\_MSA\_Operating\_Guidelines\_R1.0.pdf

# 8 MSA Mechanical

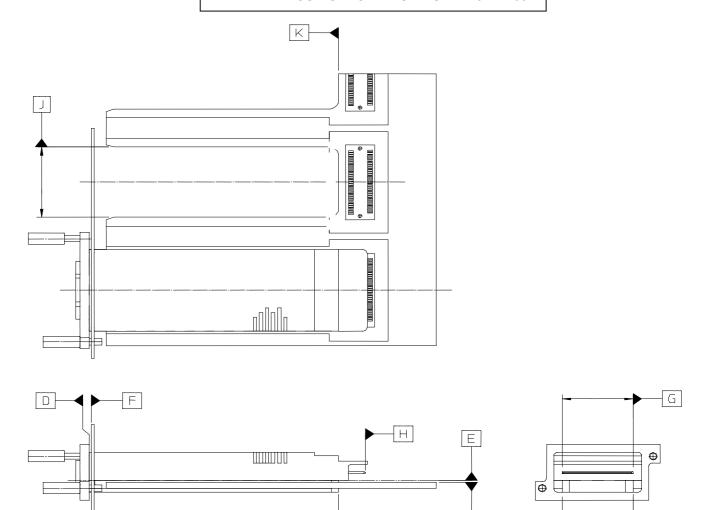

Fig 1. Isometric Drawings

Fig 2. DATUM Legend figure updated

## **ALL DRAWINGS CONFORM TO ANSI Y14.5M - 1994**

**Definition of Datums**

В

-[

| DATUM | DESCRIPTION TRANSCEIVER / LINECARD                  |

|-------|-----------------------------------------------------|

| A     | CUSTOMER'S PCB TOP SURFACE                          |

| В     | PHYSICAL HARD STOP FOR TRANSCEIVER                  |

| С     | EDGE OF TRANSCEIVER SLOT                            |

| D     | BACK SURFACE OF TRANSCEIVER BEZEL, SAFETY HARD STOP |

| E     | TRANSCEIVER TOP SURFACE OF SLOT 'P1'                |

| F     | FRONT SURFACE OF CUSTOMER'S FACEPLATE               |

| G     | EDGE OF TRANSCEIVER'S PCB                           |

| Н     | LEADING EDGE OF TRANSCEIVER PCB                     |

| J     | EDGE OF CUT-OUT IN CUSTOMER'S PCB                   |

| K     | PHYSICAL HARD STOP ON CUSTOMER'S PCB                |

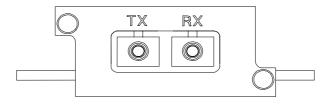

Fig 3. ORIENTATION KEYING OF TX AND RX ORIENTATION Vs PCB

XENPAK MSA Rev 3.0 Page 9 of 77

# **END VIEW OF TRANSCEIVER**

# SIDE ELEVATION TRANSCEIVER

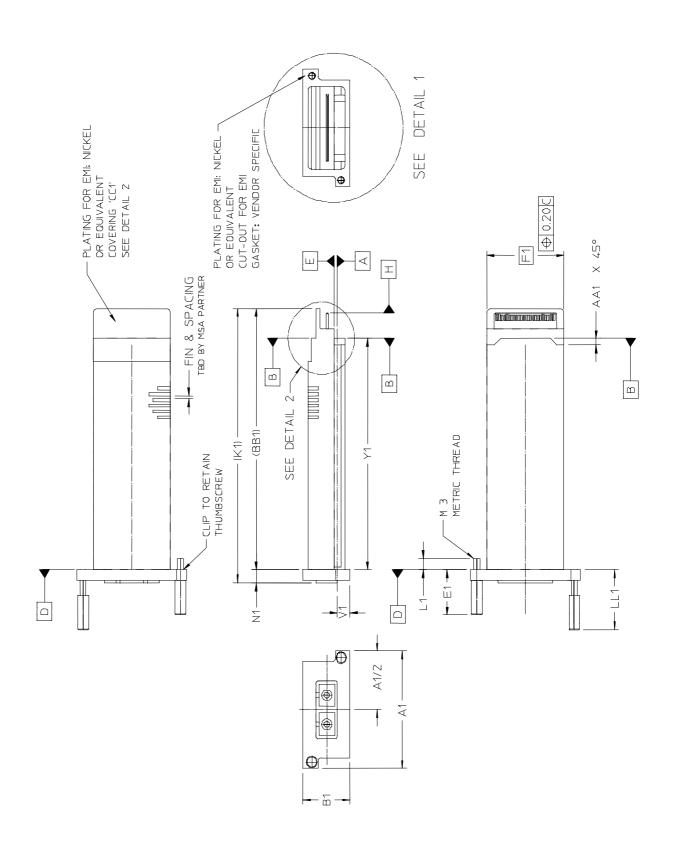

XENPAK MSA Rev 3.0 Page 11 of 77

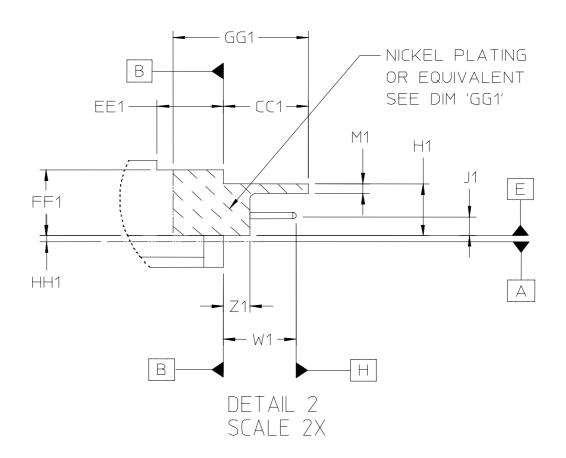

Table 1 Package Dimensions

| KEY | VALU<br>mm / i | -     | TOLERANCE<br>mm | COMMENTS                                                                                                                                        |

|-----|----------------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | 51.3           | 2.020 | ±0.20           | Width of Bezel overall                                                                                                                          |

| B1  | 22.4           | 0.882 | ± 0.20          | Height of Bezel overall                                                                                                                         |

| C1  | 45.5           | 1.791 | BASIC           | Distance between captive screws in 'X' axis (Horizontal)                                                                                        |

| D1  | 3.70           | 0.136 | BASIC           | Datum 'E' to lower captive screw                                                                                                                |

| E1  | 20.75          | 0.817 | Maximum         | Extension of captive screw                                                                                                                      |

| F1  | 36.0           | 1.417 | ± 0.20          | Width of Transceiver body                                                                                                                       |

| G1  | 17.4           | 0.685 | ± 0.20          | Height of Transceiver body                                                                                                                      |

| H1  | 8.15           | 0.331 | ± 0.20          | Datum 'E' to top of Over-hanging Ledge                                                                                                          |

| J1  | 3.05           | 0.120 | ± 0.25          | Datum 'E' to centerline of Transceiver PCB                                                                                                      |

| K1  | (121.0)        | 4.764 | REF             | Length of Transceiver overall minus protruding captive screw heads                                                                              |

| L1  | 5.00           | 0.197 | ± 0.20          | Length of captive screw from Datum 'D' to end of threaded end                                                                                   |

| M1  | 1.5            | 0.059 | ± 0.20          | Thickness of Over-hanging Ledge                                                                                                                 |

| N1  | 5.8            | 0.228 | ± 0.20          | Datum 'D' to front of Transceiver Bezel                                                                                                         |

| P1  | 4.07           | 0.160 | Minimum         | Slot or channel formed by Interposer to accommodate Customer PCB range. Use of an Interposer spring is not a requirement of this specification. |

| Q1  | 4.65           | 0.183 | ± 0.20          | Protrusion of side flange on Transceiver Bezel                                                                                                  |

| R1  | 7.12           | 0.280 | ± 0.20          | Height of side flange on Transceiver Bezel                                                                                                      |

| S1  | 29.5           | 1.161 | ± 0.20          | Width of Transceiver slot to accommodate rail or Customers PCB                                                                                  |

| T1  | 5.42           | 0.213 | BASIC           | Datum 'E' to Bottom of Transceiver                                                                                                              |

| U1  | (11.98)        | 0.481 | REF             | Datum 'E' to Top of Transceiver                                                                                                                 |

| V1  | 7.92           | 0.312 | ± 0.20          | Datum 'E' to Bottom of Transceiver Bezel                                                                                                        |

| W1  | 11.10          | 0.437 | ± 0.20          | Datum 'B' to end of protruding Transceiver PCB                                                                                                  |

| Y1  | 102.20         | 4.024 | ± 0.20          | Datum 'D' to Datum 'B'                                                                                                                          |

| Z1  | 4.0            | 0.157 | ± 0.20          | Datum 'B' to end of side protective shroud to mate with EMI/Conn. Shield                                                                        |

| AA1 | 3.0            | 0.118 | ± 0.50          | Datum 'B' to end of 45° chamfer                                                                                                                 |

| BB1 | (115.2)        | 4.535 | REF             | Length of Module from Datum 'D' to rear Over-hanging Ledge                                                                                      |

| CC1 | 13.0           | 0.512 | ± 0.50          | Datum 'B' to end of Over-hanging Ledge for EMI Plating                                                                                          |

| DD1 | 13.96          | 0.550 | BASIC           | Distance between captive screws in 'Y' axis (Vertical)                                                                                          |

| EE1 | 10.0           | 0.394 | Minimum         | Datum 'B' end of recess for insertion clearance                                                                                                 |

| FF1 | 10.48          | 0.422 | ± 0.50          | Datum 'E' to Top of recess for insertion clearance                                                                                              |

| GG1 | 20.0           | 0.787 | Minimum         | Length of Transceiver side wall for EMI plating                                                                                                 |

| HH1 | 0.25           | 0.01  | Basic           | Datum 'A' to Datum 'E'                                                                                                                          |

| JJ1 | 29.2           | 1.150 | ± 0.10          | Width of Transceiver PCB                                                                                                                        |

| KK1 | 3.0            | 0.118 | N/A             | Hole for 3mm screw Thumbscrew, tapped or clearance                                                                                              |

| LL1 | 25.8           | 1.016 | Maximum         | Length of Thumbscrew                                                                                                                            |

| RA1 | 1.25           | 0.049 | Minimum         | External radius or chamfer of Transceiver                                                                                                       |

| RB1 | 1.5            | 0.059 | Maximum         | Internal radius or chamfer on exterior flange of Transceiver Bezel                                                                              |

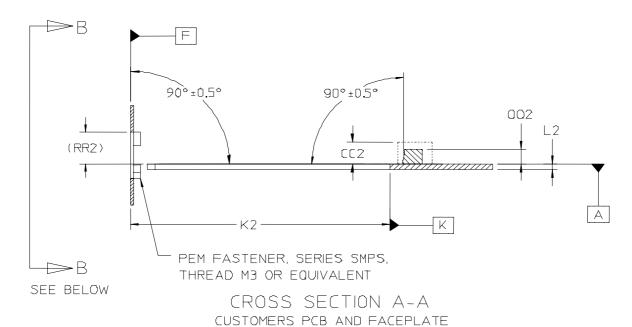

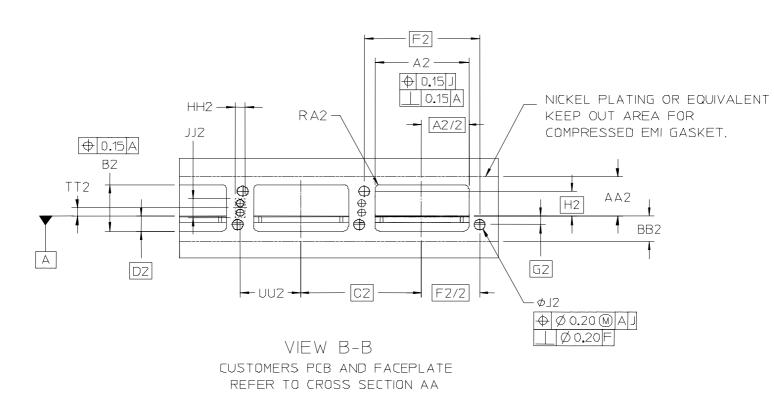

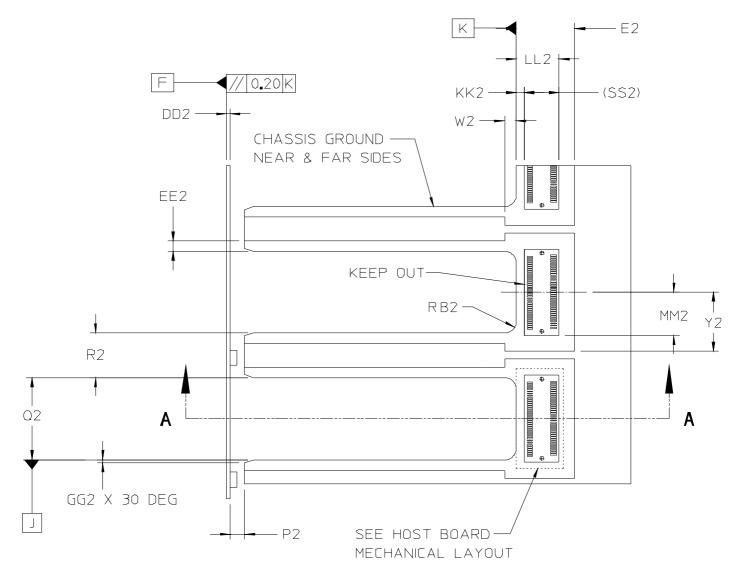

Fig 5. Front Panel Opening and Host PCB

#### Refer to Table 2 for Dimensions

Fig 5(cont'd)

## Refer to Table 2 for Dimensions

# PLAN VIEW CUSTOMERS PCB

Table 2

Front Panel Opening and Host PCB Dimensions

| KEY | VALUES<br>mm / Inch     | TOLERANCE<br>mm | COMMENTS                                                                         |

|-----|-------------------------|-----------------|----------------------------------------------------------------------------------|

| A2  | 37.0 1.457              | ± 0.20          | Width of cut-out of Customers sheet metal Faceplate                              |

| B2  | 18.6 0.732              | ± 0.20          | Cut-out in Customers sheet metal Faceplate 'Y' Axis (Vertical)                   |

| C2  | 47.47 1.869             | BASIC           | Minimum Spacing of Modules in 'X' Axis (Horizontal)                              |

| D2  | 5.77 0.227              | BASIC           | Datum 'A' to bottom cut-out of the Customers sheet metal Faceplate               |

| E2  | 20.59 0.811             | ± 0.30          | Datum 'K' far side of Chassis Ground                                             |

| F2  | 45.50 1.791             | BASIC           | Distance between holes for captive fastener in 'X' Axis (Horizontal)             |

| G2  | 3.45 0.136              | BASIC           | Datum 'A' to lower mounting hole in Customers sheet metal Faceplate              |

| H2  | 10.51 0.414             | BASIC           | Datum 'A' to upper mounting hole in Customers sheet metal Faceplate              |

| J2  | 4.24 0.167              | -0.0/+0.08      | Diameter of hole for Self Clinching Nut                                          |

| K2  | 101.6 4.00              | ± 0.50          | Datum 'K' to front of Customers sheet metal Faceplate Datum F                    |

| L2  | 2.36 / 3.62 0.093/0.143 | N/A             | Customers PCB thickness range                                                    |

| M2  | 16.50 0.650             | ± 0.20          | Datum 'K' to back of Keep-out for EMI Compliant Shield                           |

| N2  | 37.00 1.457             | ± 0.20          | Width of inside surface of Connector/EMI Shield                                  |

| P2  | 6.35 0.250              | ± 0.50          | Distance from edge of customers PCB to inside surface of Customers S/M Faceplate |

| Q2  | 30.5 1.201              | ± 0.20          | Width of Slot in Customers PCB                                                   |

| R2  | 16.72 0.658             | Minimum         | Width of support on Customers PCB                                                |

| V2  | 9.00 0.354              | BASIC           | Datum 'K' to Connector mounting hole                                             |

| W2  | 4.00 0.157              | ± 0.20          | Datum 'K' to front keep-out pad for EMI Shield                                   |

| Y2  | 22.30 0.878             | ± 0.20          | Datum 'J' to side keep-out pad for EMI Shield                                    |

| AA2 | 16.2 0.638              | Minimum         | Datum 'A' to upper Keep-out on Customers sheet metal Faceplate                   |

| BB2 | 9.2 0.362               | Minimum         | Datum 'A' to lower Keep-out on Customers sheet metal Faceplate                   |

| CC2 | 8.90 0.350              | ± 0.20          | Datum 'A' to Top of Keep-out for EMI Compliant Shield                            |

| DD2 | 0.63 / 2.00 0.025/0.079 | N/A             | Thickness of Customers sheet metal Faceplate                                     |

| EE2 | 4.00 0.157              | Minimum         | Width PCB Grounding; Proposed: Immersion Gold on Nickel; Near and Far side       |

| FF2 | 1.55 0.061              | ± 0.05          | Hole Diameter for mounting Connector                                             |

| GG2 | 3.00 0.118              | ± 0.20          | Lead in Chamfer on Customers PCB                                                 |

| HH2 | 4.00 0.157              | ± 0.30          | Width of reserved space for LED bank                                             |

| JJ2 | 7.00 0.275              | ± 0.30          | Height of reserved space for LED bank                                            |

| KK2 | 2.90 0.114              | ± 0.30          | Datum 'K' to front of reserved space for Connector Pads                          |

| LL2 | 15.00 0.590             | ± 0.30          | Datum 'K' to back of reserved space for Connector Pads                           |

| MM2 | 16.30 0.642             | ± 0.30          | Datum 'J' to side of reserved space for Connector Pads                           |

| QQ2 | 5.90 0.232              | Maximum         | Datum 'A' to top of Connector                                                    |

| RR2 | (12.83) (0.505)         | REF             | Datum 'A' to top of cut-out in Customers Faceplate                               |

| SS2 | (12.1) (0.476)          | REF             | Depth of surface mount connector keep-out area.                                  |

| TT2 | 3.50 0.138              | BASIC           | Height from Datum 'A' to centerline of LED bank                                  |

| UU2 | 23.7 0.933              | ± 0.50          | Distance from centerline of Customers Slot to centerline of LED bank             |

| RA2 | 1.25 0.049              | Maximum         | Radius of opening in Customers sheet metal Faceplate                             |

| RB2 | 4.00 0.157              | Maximum         | Radius on Cut-out on Customers PCB                                               |

#### 8.1 Transceiver Printed Circuit Board

A typical contact pad plating for the printed circuit board is 0.38 micrometers minimum hard gold over 1.27 micrometers minimum thick nickel. Other plating options that meet the performance requirements are acceptable. See Fig 17 for electrical signal pin out.

H 3.50 MINIMUM - 1.30 ± Q.10 G 0.50 ±0.10 [4X] 0.80 [34X] 14.60 13.80 29.20 TDP VIEW OF BOARD 13.40 0.60±0.05 + 0.10 G 0.50 X 45 DEG 1 0.10 H [35X] [2X] 0.30 X 45° [2X] 1.00 ±0.10 -OVER PADS Н 3,50 MINIMUM 1.30 ±0.10 0.50 ±0.10 [10X] 0.80 [34X] 13.80 BOTTOM VIEW OF BOARD 13,40 0.60±0.D5 + 0.10 G [35X] \_\_\_ Q.10 H

Fig 6. Transceiver Printed Circuit Board Connector

# 8.2 Host Board Mechanical Layout

See Fig 18 for electrical signal pin out.

PAD DETAIL Scale 4:1 XENPAK MSA Rev 3.0 Page 17 of 77

# 8.3 Electrical Connector

See Fig 18 for electrical signal pin out.

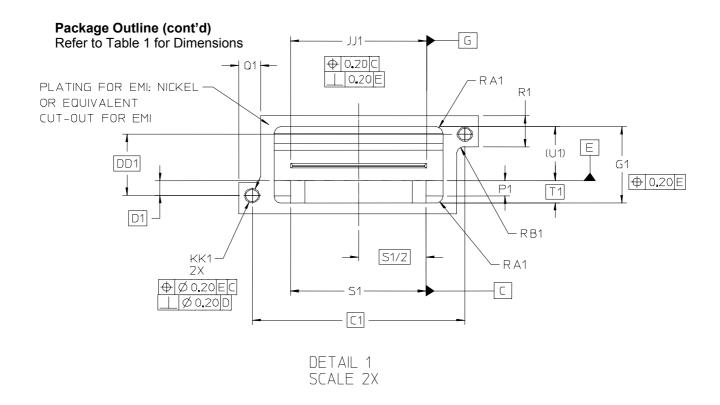

Fig 8. Connector Drawing

Table 3 **Connector Dimensions**

| Key | Dim. (mm) | Tolerance | COMMENTS                                                     |  |

|-----|-----------|-----------|--------------------------------------------------------------|--|

| Α   | 29.4      | ±0.08     | Connector card slot                                          |  |

| В   | 1.4       | ±0.05     | Guide pin diameter                                           |  |

| С   | 31.2      | Maximum   | Connector width                                              |  |

| D   | 9.2       | Maximum   | Connector Length                                             |  |

| Е   | 13.5      | Reference | Distance from centerline of connector to outer contact       |  |

| F   | 13.9      | Reference | Distance from centerline of connector to outer contact       |  |

| G   | 1.35      | Maximum   | Connector card slot height                                   |  |

| Н   | 2.6       | Minimum   | Height from bottom of connector to bottom of card slot       |  |

| J   | 29.6      | TP        | Distance between guide pins                                  |  |

| K   | 0.9       | Reference | Diamond guide pin width, NOT SHOWN                           |  |

| L   | 1.4       | ±0.05     | Diamond guide pin length, NOT SHOWN                          |  |

| М   | 5.9       | Maximum   | Connector height                                             |  |

| N   | 0.8       | Reference | Length of solder leads past housing, front and rear          |  |

| Р   | 6.0       | Minimum   | Depth of card slot from front face of housing                |  |

| Q   | 3.0       | Maximum   | Depth of contact point from front face of connector          |  |

| R   | 0.7       | ±0.01     | Size of chamfer on top of connector, NOT SHOWN               |  |

| S   | 0.3       | Reference | Distance boss extends past front face of connector           |  |

| Т   | 0.6       | Minimum   | Size of chamfer at entry of card slot, all around, NOT SHOWN |  |

| U   | 4.5       | Reference | Length from centerline of guide posts to end of solder lead  |  |

#### 8.4 Optical Interface

The objective of this section is to specify the optical connector interface to sufficiently insure performance, inter-mateability and maximum supplier flexibility.

## 8.4.1 Optical Plug:

The optical interface shall use a duplex SC optical plug that conforms to IEC 61754-4. Only the floating duplex style connector plug shall be used. Rigid SC duplex connectors shall not be used. Connector keys are used for transmit / receive polarity.

NOTE: Floating Duplex SC Connectors use two simplex connectors and mechanically couple them together to create 1 connector that retains both, but allows both connectors to 'float', within the specified tolerance.

### 8.4.2 Optical Receptacle:

The SC Duplex Receptacle shall conform to the requirements of IEC 61754-4with the following clarification:

The distance between the centerline of the active optical bores (ref DB) shall be 12.25/13.15mm to match the floating duplex SC optical plug (ref Duplex optical plug table Note 8).

Increasing this tolerance avoids the restrictive manufacturing tolerance associated with rigid SC connectors.

#### 8.5 Mechanical Forces

The following limits should be observed when designing for, or using, XENPAK transceivers:

Maximum insertion force = 80 N (Includes connector, interposer and connector shield ground spring)

Maximum extraction force = 50 N

Minimum retention force (with screws engaged) = 130 N

Fastener Torque: 0.1 Nm (3mm captive screw)

#### 8.6 Transceiver and Connector Durability

The following life ratings should be observed when designing for, or using, XENPAK transceivers and their associated connectors:

Minimum mate/de-mate cycles for transceiver = 50 cycles

Minimum mate/de-mate cycles for 70-pin connector = 100 cycles

# 9 XENPAK Thermal Requirements

# 9.1 Maximum power dissipation

Transceivers with 850nm or 1310nm PMD will dissipate a maximum of 6W. Transceivers with 1550nm PMD will dissipate a maximum of 10W.

# 9.2 Maximum case temperature

Maximum case temperature for a XENPAK module is 70 C. Case temperature is as defined in IEC 60950 section 4.5.1 and table 4B

Maximum case temperature of 70°C is specified for systems with 8 or fewer adjacent 850nm or 1310nm modules.

Maximum case temperature of 70°C is specified for systems with 4 or fewer adjacent 1550nm modules.

Case temperature is not specified for systems with mixed PMD types (850/1310/1550nm). Individual characterization of systems with mixed PMD types is recommended.

See Appendix 1A for recommended test parameters used in verification of module thermal performance.

#### 10 XENPAK Electrical Interface

A XENPAK module will be functionally operational within 5 second of insertion. Parametric performance (such as laser line width) may depend on thermal stabilization of the module and may take substantially longer and will depend on the thermal environment imposed by the host.

# 10.1 Power Supplies and Hot Swapping

5.0V, 3.3V and an Adaptable Power Supply rail (APS) should be supplied to a XENPAK transceiver through the transceiver connector. During module insertion chassis ground connects first to the customer chassis via the chassis areas defined in **Fig 5** on the host board. The first electrical connector pins to make contact are Electrical Ground and APS power followed by VCC and Signal contacts. The 10G transceiver should tolerate biasing of signal contacts in the absence of VCC.

## 10.2 Grounding

Chassis and electrical ground will be DC-isolated. They may be connected in the host chassis at the option of the chassis designers.

# 10.3 Adaptable Power Supply

Fig 9. Adaptable Power Supply

The Back-plane will provide an adaptable power supply capable of adjusting from a high of 1.8 volts to a low of 0.9 volts.

The XENPAK module shall support a voltage sense pin for the APS on the "APS Sense" pin. The XENPAK module shall incorporate a resistor R1, between the "APS Set" pin and ground. Resistor values, corresponding to the required voltage, shall be as in Table 4.

If the pin used for APS SET is shorted to ground on the module, the APS will default to a fixed 1.8 volts.

The signal contact pin #14 "MOD DETECT" may be used to enable the APS power when the module is installed. The host design may also take control of the APS supply enable pin via software or some other mechanism.

The Adaptable supply can compensate for undesired voltage drops across the host PCB the XENPAK connector and potentially inside the XENPAK module itself (implementation dependent).

Because the APS sense does not compensate for voltage drops on the ground plane and ground pins of the connector, it is important that the ground path has a very low voltage drop, 1% is used in the tolerance analysis.

The host will provide < 200 mV to the adaptable voltage rail when no XENPAK module is installed and will ramp up to the requested voltage and be within specification within 500 ms of full insertion.

The APS is intended to default to a low voltage output if any single pin makes a poor connection, specifically:

- If the APS SET pin is connected and the APS Sense pin is open, the APS supply will put out near zero volts due to the 500 Ohm pull-up resistor to 3.3 volts (see Fig 10).

- If the APS Sense is connected and the APS SET connection is open,, the supply defaults to low voltage of 0.8 volts.

- If both the APS SET and APS Sense connections are open, the APS supply will put out near zero volts.

The APS supply leads are elongated to prevent a condition where the SENSE lead connects before the APS supply leads and pulls down the SENSE pin resulting in an instantaneous high voltage from the APS, before the module is fully seated.

# 10.3.1 Adaptable Power supply reference

The APS supply on the host will regulate the APS voltage such that the voltage on the network labeled "Vfeedback" in Fig 10 becomes nominally 0.8 volts unless an APS voltage or current limiting

condition takes priority. The resistors in the following table are calculated using resistors available as 1% values. For tolerance purposes, it is recommended that 0.1% resistors are used to provide additional tolerance margin although 1% may be suitable for some applications. These values are subject to change after a host back-plane is built and tested.

Table 4 Resistor Values for APS operation.

| Vnom volts | R1 ohms |

|------------|---------|

| 0.9        | 6810    |

| 1          | 3160    |

| 1.1        | 1820    |

| 1.2        | 1180    |

| 1.3        | 806     |

| 1.4        | 536     |

| 1.5        | 348     |

| 1.6        | 210     |

| 1.7        | 97.6    |

| 1.8        | 0       |

The resistor values given in Table 4 place the nominal set-point slightly high, to help compensate for some of the anticipated ground plane drop.

Table 5 Recommended Tolerances (+/-)

| Supply precision                       | <u>1.5%</u> |

|----------------------------------------|-------------|

| Supply load regulation                 | 0.3%        |

| Ground plane and ground connector drop | <u>1.0%</u> |

| Resistor tolerances using 0.1% parts   | 0.3%        |

| Margin                                 | 0.9%        |

| Total APS tolerance (+/-)              | 4.0%        |

## 10.3.2 Voltage calculation

The circuit shown in Fig 10, depicts conceptually the design used to generate the APS voltage. Exact implementation and component values are not mandatory on the host. The APS implementer is responsible for ensuring that the XENPAK module is supplied in a manner which conforms to the APS tolerances stated in Table 5 for any given resistance between the module set pin and module ground.

## 10.3.3 Current capability of the APS

The APS will provide from 0.1 to 1.8 amperes and will current limit at typically 2 to 4 amperes.

# 10.3.4 Adaptable Power Supply Specs/Requirements

The host PCB will provide a steady state voltage on the adaptable voltage power conforming to the specifications given in Table 5.

Table 6 APS Tolerances (+/-)

| APS steady state RMS ripple                                  | <40mV rms            |  |  |

|--------------------------------------------------------------|----------------------|--|--|

| APS tolerance for a given resistance from APS set to ground. | <u>+/- 3%</u>        |  |  |

| APS max overshoot after insertion/host power up              | 3% of V steady state |  |  |

| APS min rated current                                        | <u>0.1 Amps</u>      |  |  |

| APS maximum rated current for any voltage                    | <u>1.8 Amps</u>      |  |  |

| APS current limit                                            | 2 ->4 Amps           |  |  |

| XENPAK total capacitance of transceiver APS power pins       | <200 uF              |  |  |

# 10.4 Fixed Voltage Supply Specs and Inrush Currents

These specifications shall be applicable to the fixed 3.3V and 5.0V supply rails. The inrush current on any fixed supply rail during hot plug or power up in host of a XENPAK module shall be limited by the XENPAK module to assure a maximum rate of change de fined in Table 7. The peak inrush currents to any supply rail shall not exceed the steady state currents for that rail by more than 50%.

Ramp up time controlled by the XENPAK module shall allow operation within 5 seconds after the adaptable power supply back-plane has stabilized as required above.

| Steady State Voltage Accuracy               | +/-5% of rated                    |

|---------------------------------------------|-----------------------------------|

| Steady state RMS ripple (max)               | 40mV rms                          |

| Stabilization time to rated tolerance (max) | < 500 ms                          |

| Inrush current during hot plug max          | <u>50 mA/ms</u>                   |

| Inrush current (per power pin) max          | <0.75A                            |

|                                             | (150% x 0.5A steady state rating) |

Table 7 Fixed Power Rail Tolerances (+/-)

A XENPAK module inserted in this system shall inject <20mV rms ripple onto any fixed voltage rail when supplied from a "near ideal" voltage source followed by a 5 ohm series resistor.

#### 10.4.1 Hot Swap and Transceiver Power-On-Reset Definition

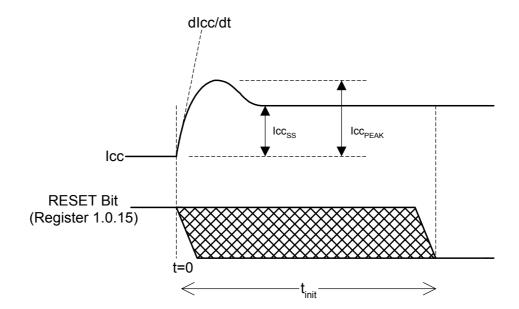

When a 10G transceiver is inserted the ramp rate of supply current must also comply with the specification in Table 8. Control of inrush current (as shown in Fig 14) should be internal to the XENPAK transceiver

The 10G transceiver shall achieve a stable state of normal operation after mechanical insertion at time, t=0 according to the following specification.

| Parameter           | Symbol              | Min. | Тур. | Max. | Units |

|---------------------|---------------------|------|------|------|-------|

| Icc Peak Inrush     | ICC <sub>PEAK</sub> | -    | -    | 50   | %     |

| Icc Ramp rate       | dICC/dt             | -    | -    | 50   | mA/ms |

| Initialisation Time | t <sub>init</sub>   | -    | -    | 5    | S     |

Table 8 Power on Reset characteristics

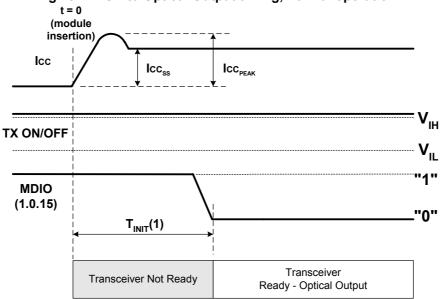

# 10.4.2 Low Power Start-up (LPS) Mode

Low power startup is an optional feature of XENPAK modules. A transceiver will indicate it's LPS ability by setting bit 0 of the Optional Capability Register (see Section 10.12.21) to 1 if implemented and 0 otherwise.

If LPS is implemented the module will only initialize the MDIO-functionality, and limit the power consumption to a fraction of normal levels, typical less than 1W.

For LPS to be invoked, the system shall pull the signal TX ON/OFF (pin 12) low, for all the empty module slots and hold it low after a module is inserted, until the system reads the modules registers and establishes what it's respective thermal and power needs. The system can thereby establish if the newly inserted module causes it to exceed it's thermal or power supply capacity and to reject the module, by holding it in a low power state until it does. Otherwise the system enables the module to commence normal operation, by raising the TX ON/OFF signal.

The XENPAK NVR contains pre-programmed power supply requirement information for an LPS enabled module, as detailed in Table 1.

The LPS feature is particularly relevant to longer reach XENPAKs which may load power supplies and cooling more than shorter reach parts, but which are not typically inserted into all ports of a line card.

Four measurements are made on a representative sample of part of a representative build standard in the MSA thermal test chamber described in Section 12.

#### Specific parameters are:

- 5V Stressed Environment Reference (100% = 1A)

- 3.3V Stressed Environment Reference (100% = 2A)

- APS Stressed Environment Reference (100% = 2A)

- Nominal APS Voltage

#### Under the following conditions:

One module is inserted in the test fixture middle slot (number four or five) with the remaining front openings closed with blanking plates. An inlet air temperature of 50°C and airspeed of 2 m/s shall be used for the single stressed environment current reference measurement on each rail.

Mandatory reference values are written into the NVR Basic Space in the format shown in Table 1.

# 10.5 Transceiver Monitoring

Contacts are available on the module connector for Link Alarm Status Interrupt (LASI). A module detect pin allows hardware detection of a module when it is inserted into a customer chassis. This pin is pulled through  $1k\Omega$  to GND inside the module and can be used to drive an interrupt for polling-free module detection.

The 2-wire Management Data I/O interface (802.3ae Clause 45) is mandatory in the XENPAK MSA. MDC provides clocking for the data that is passed on the MDIO line. Five further pins allow for loading of a Port Address (PRTAD0-4) into the module.

Fig 11. Functional Diagram of Typical XENPAK Style Transceiver

## 10.5.1 High Speed Signals

The XAUI transmit and receive data complies with IEEE802.3ae Clause 47 electrical specification, which should be referenced for actual values. AC coupling is provided inside the module for both transmit and receive directions as indicated in Fig 12. For clarity only one TX and RX XAUI lane is shown. The impedance of Zin is 100 Ohms differential.

Fig 12. High Speed Signals

XENPAK MSA Rev 3.0 Page 27 of 77

# 10.5.2 Low Speed Signals

Low Speed Signals, as indicated in Table 11, are open drain compatible to permit wired 'OR' connections. Pull up resistors are provided in the transceiver or on the host board according to Fig 13.

Fig 13. Example of Low Speed Output Configuration

Example of one termination configuration only is given. See Table 11 and Table 12 for exact description of terminations required for each signal.

**Parameter** Min Max Units Notes Тур 1.2V CMOS 0.36  $V_{IL(MAX)}$ 0.84 1.25 1.2V CMOS  $V_{IH(MIN)}$ -٧ Maximum Fan-out of 32. Capacitance 320 pF 10pF per port 10k 22k Pull Up Resistance Ω

Table 9 Electrical Characteristics of Low Speed Interface

#### 10.5.3 Initialisation and Reset

After successful plug in and initialization sequence the transceiver should clear MDIO Bit register N.0.15 (Where N= any implemented device). A timing diagram is in Fig 14. The transceiver may be reset in situ using the hardware reset pin or MDIO register bit 1.0.15 according to Table 10.

**When reset** using the hardware reset pin or by setting Bit 15 in MDIO register 1.0 the transceiver should initialize and then clear MDIO Bit N.0.15.

Fig 14. Initialisation and Hot Swap Timing Diagram

Table 10 Relationship between the TRANSCEIVER RESET pin and MDIO Reset Bit

| RESET Pin | MDIO Register Pin Condition Transceiver Behavi 1.0.15 |                                                               |

|-----------|-------------------------------------------------------|---------------------------------------------------------------|

| 1         | 0                                                     | Normal operation                                              |

| 0         | 0                                                     | Transient state between RESET PIN low and 1.0.15 getting set  |

| 1         | 1                                                     | Reset State                                                   |

| 0         | 1                                                     | State assumed shortly after Transceiver reset pin pulled low. |

#### 10.5.4 Tx On/Off

The timing relationship between Tx on/off and the optical output is shown in Fig 15. The optical output will turn off within 100us of Tx ON/OFF being pulled low.

Fig 15. Tx Off to Optical Output timing, normal operation.

## **10.6 Multiple PMD Support**

This MSA aims to accommodate all four 10Gb PMDs and both LAN and WAN PHY variants (apart from LX4 which is not defined for WAN PHY).

LX4 Wavelengths will always be mapped to the XAUI per IEE 802.3ae, Clause 53, Table 53–5

#### 10.7 Electrical Connector

The XENPAK connector is a 70-way two-row connector, similar in style to the 20-way SFP connector. (examples are TycoAMP Part No. 1367337-1 and Molex Part No. 74441-0003, or equivalent. Exact choice of connectors may depend on environment, contact manufacturer for detail )

The 10G transceiver PCB forms one mating half of the connector.

Pin definitions are listed in Table 11 and Table 12.

Mechanical dimensions for the transceiver Electrical Pad Layout and Host board are shown in Fig 6, Fig 7 and Fig 8,. Signal layouts are shown in Fig 17 and Fig 18.

#### 10.7.1 ESD

Human Body Model survivability is recommended to a minimum of 500V, measured to MIL STD 883 Method 3015.1. End of row contacts on the transceiver connector are ground connections so that I/O pins will not be subjected to the highest Charged Device Model (CDM) ESD test voltage, if applicable.

Table 11 Pin Function Definitions (Lower Row)

| Pin No   | Name                 | Dir      | Function                                                | Notes |

|----------|----------------------|----------|---------------------------------------------------------|-------|

| 1        | GND                  |          | Electrical Ground                                       | 1     |

| 2        | GND                  |          | Electrical Ground                                       | 1     |

| 3        | GND                  |          | Electrical Ground                                       | 1     |

| 4        | 5.0V                 |          | Power                                                   | 2     |

| 5        | 3.3V                 |          | Power                                                   | 2     |

| 6        | 3.3V                 |          | Power                                                   | 2     |

| 7        | APS                  |          | Adaptive Power Supply                                   | 2     |

| 8        | APS                  |          | Adaptive Power Supply                                   | 2     |

| 9        | LASI                 |          | Open Drain Compatible                                   | 4     |

|          |                      |          | 10K-22K pull up on host.                                |       |

|          |                      |          | Logic High: Normal Operation                            |       |

| 40       | DECET                |          | Logic Low: LASI Asserted                                |       |

| 10       | RESET                | I        | Open Drain compatible.                                  | 4     |

|          |                      |          | 10-22K pull-up on transceiver                           |       |

|          |                      |          | Logic high = Normal operation Logic low = Reset         |       |

|          |                      |          | Minimum reset assert time 1 ms                          |       |

| 11       | VEND SPECIFIC        |          | Vendor Specific Pin.                                    | 8     |

| ' '      | VEND SI LOII IC      |          | Leave unconnected when not in use.                      | 0     |

| 12       | TX ON/OFF            | 1        | Open Drain compatible.                                  | 4     |

| '-       | 17.014.011           |          | 10-22K pull-up on transceiver                           | '     |

|          |                      |          | Logic high = Transmitter On (capable)                   |       |

|          |                      |          | Logic low = Transmitter Off (always)                    |       |

| 13       | RESERVED             |          | Reserved                                                | 4     |

|          |                      |          |                                                         |       |

| 14       | MOD DETECT           | 0        | Pulled low inside module through 1k                     |       |

| 15       | VEND SPECIFIC        |          | Vendor Specific Pin.                                    | 8     |

|          |                      |          | Leave unconnected when not in use.                      |       |

| 16       | VEND SPECIFIC        |          | Vendor Specific Pin.                                    | 8     |

|          | 11010                |          | Leave unconnected when not in use.                      |       |

| 17       | MDIO                 | I/O      | Management Data IO                                      | 4, 5  |

| 18       | MDC                  | !        | Management Data Clock                                   | 4, 5  |

| 19       | PRTAD4               | !        | Port Address Bit 4 (Low = 0)                            | 4     |

| 20       | PRTAD3               |          | Port Address Bit 3 (Low = 0)                            | 4     |

| 21       | PRTAD2               |          | Port Address Bit 2 (Low = 0)                            | 4     |

| 22       | PRTAD0               | <u> </u> | Port Address Bit 1 (Low = 0)                            | 4     |

| 23<br>24 | PRTAD0 VEND SPECIFIC | !        | Port Address Bit 0 (Low = 0)                            | 8     |

| 24       | VEIND SPECIFIC       |          | Vendor Specific Pin. Leave unconnected when not in use. | 0     |

| 25       | APS SET              |          | Feedback input for APS                                  |       |

| 26       | RESERVED             |          | Reserved for Avalanche Photodiode use.                  | 8     |

| 27       | APS SENSE            |          | APS Sense Connection                                    |       |

| 28       | APS                  |          | Adaptive Power Supply                                   | 2     |

| 29       | APS                  |          | Adaptive Power Supply  Adaptive Power Supply            | 2     |

| 30       | 3.3V                 |          | Power                                                   | 2     |

| 31       | 3.3V                 |          | Power                                                   | 2     |

| 32       | 5.0V                 |          | Power                                                   | 2     |

| 33       | GND                  |          | Electrical Ground                                       | 1     |

| 34       | GND                  |          | Electrical Ground                                       | 1     |

| 35       | GND                  | +        | Electrical Ground                                       | 1     |

Table 12 Pin Function Definitions (Upper Row)

| Pin No | Name      | Dir | Function                   | Notes |

|--------|-----------|-----|----------------------------|-------|

| 36     | GND       |     | Electrical Ground          | 1     |

| 37     | GND       |     | Electrical Ground          | 1     |

| 38     | RESERVED  |     | Reserved                   |       |

| 39     | RESERVED  |     | Reserved                   |       |

| 40     | GND       |     | Electrical Ground          | 1     |

| 41     | RX LANE0+ | 0   | Module XAUI Output Lane 0+ | 7     |

| 42     | RX LANE0- | 0   | Module XAUI Output Lane 0- | 7     |

| 43     | GND       |     | Electrical Ground          | 1     |

| 44     | RX LANE1+ | 0   | Module XAUI Output Lane 1+ | 7     |

| 45     | RX LANE1- | 0   | Module XAUI Output Lane 1- | 7     |

| 46     | GND       |     | Electrical Ground          | 1     |

| 47     | RX LANE2+ | 0   | Module XAUI Output Lane 2+ | 7     |

| 48     | RX LANE2- | 0   | Module XAUI Output Lane 2- | 7     |

| 49     | GND       |     | Electrical Ground          | 1     |

| 50     | RX LANE3+ | 0   | Module XAUI Output Lane 3+ | 7     |

| 51     | RX LANE3- | 0   | Module XAUI Output Lane 3- | 7     |

| 52     | GND       |     | Electrical Ground          | 1     |

| 53     | GND       |     | Electrical Ground          | 1     |

| 54     | GND       |     | Electrical Ground          | 1     |

| 55     | TX LANE0+ | I   | Module XAUI Input Lane 0+  | 7     |

| 56     | TX LANE0- | 1   | Module XAUI Input Lane 0-  | 7     |

| 57     | GND       |     | Electrical Ground          | 1     |

| 58     | TX LANE1+ | I   | Module XAUI Input Lane 1+  | 7     |

| 59     | TX LANE1- | I   | Module XAUI Input Lane 1-  | 7     |

| 60     | GND       |     | Electrical Ground          | 1     |

| 61     | TX LANE2+ | 1   | Module XAUI Input Lane 2+  | 7     |

| 62     | TX LANE2- | I   | Module XAUI Input Lane 2-  | 7     |

| 63     | GND       |     | Electrical Ground          | 1     |

| 64     | TX LANE3+ | 1   | Module XAUI Input Lane 3+  | 7     |

| 65     | TX LANE3- | 1   | Module XAUI Input Lane 3-  | 7     |

| 66     | GND       |     | Electrical Ground          | 1     |

| 67     | RESERVED  |     | Reserved                   |       |

| 68     | RESERVED  |     | Reserved                   |       |

| 69     | GND       |     | Electrical Ground          | 1     |

| 70     | GND       |     | Electrical Ground          | 1     |

#### Notes:

- 1) Ground connections are common for TX and RX.

- 2) All connector contacts are rated at 0.5A nominal.

- 4) 1.2V CMOS compatible.

- 5) MDIO and MDC timing must comply with IEEE802.3ae, Clause 45.3

- 7) XAUI output characteristics should comply with IEEE802.3ae Clause 47.

- 8) Transceivers will be MSA compliant when no signals are present on the vendor specific pins.

Fig 17. XENPAK Transceiver Electrical Pad Layout

|   |              | 70      | GND       |    |               |

|---|--------------|---------|-----------|----|---------------|

|   |              |         |           | 1  | GND           |

|   |              | 69      | GND       | 2  | GND           |

|   |              | 68      | RESERVED  | 3  | GND           |

|   |              | 67      | RESERVED  | 4  | 5.0V          |

|   |              | 66      | GND       | 5  | 3.3V          |

|   |              | 65      | TX LANE3- | 6  | 3.3V          |

|   |              | 64      | TX LANE3+ | 7  | APS           |

|   |              | 63      | GND       | 8  | APS           |

|   |              | 62      | TX LANE2- | 9  | LASI          |

|   |              | 61      | TX LANE2+ | 10 | RESET         |

|   |              | 60      | GND       | 11 | VEND SPECIFIC |

|   |              | 59      | TX LANE1- | 12 | TX ON/OFF     |

|   |              | 58      | TX LANE1+ | 13 | RESERVED      |

|   |              | 57      | GND       | 14 | MOD DETECT    |

|   | 1            | 56      | TX LANE0- | 15 | VEND SPECIFIC |

|   |              | 55<br>1 | TX LANE0+ | 16 | VEND SPECIFIC |

|   | Toward Bezel | 54      | GND       | 17 | MDIO          |

| \ |              | 53      | GND       | 18 | MDC           |

|   |              | 52      | GND       | 19 | PRTAD4        |

|   |              | 51      | RX LANE3- | 20 | PRTAD3        |

|   |              | 50      | RX LANE3+ | 21 | PRTAD2        |

|   |              | 49      | GND       | 22 | PRTAD1        |

|   |              | 48      | RX LANE2- | 23 | PRTAD0        |

|   |              | 47      | RX LANE2+ | 24 | VEND SPECIFIC |

|   |              | 46      | GND       | 25 | APS SET       |

|   |              | 45      | RX LANE1- | 26 | RESERVED      |

|   |              | 44      | RX LANE1+ | 27 | APS SENSE     |

|   |              | 43      | GND       | 28 | APS           |

|   |              | 42      | RX LANE0- | 29 | APS           |

|   |              | 41      | RX LANE0+ | 30 | 3.3V          |

|   |              | 40      | GND       | 31 | 3.3V          |

|   |              | 39      | RESERVED  | 32 | 5.0V          |

|   |              | 38      | RESERVED  | 33 | GND           |

|   |              | 37      | GND       | 34 | GND           |

|   |              | 36      | GND       | 35 | GND           |

|   |              |         |           |    |               |

**Top of Transceiver PCB**

**Transceiver PCB**

(as viewed through

**Bottom of**

top)

Note: Refer to Fig 6

Ground pins 1, 2, 3, 33, 34, 35, 36, 37, 69, 70 and APS power pins 7, 8, 28, 29, are extended so as to make contact first upon XENPAK insertion.

GND 70 GND 1 GND 69 2 GND RESERVED 68 3 GND RESERVED 67 4 5.0V GND 66 5 3.3V TX LANE3-65 6 3.3V TX LANE3+ 64 7 GND 63 8 APS TX LANE2-62 9 LASI TX LANE2+ 61 10 RESET GND 60 VEND SPECIFIC 11 TX LANE1-59 12 TX ON/OFF TX LANE1+ 58 RESERVED 13 GND 57 MOD DETECT 14 TX LANE0-56 15 VEND SPECIFIC TX LANE0+ 55 16 VEND SPECIFIC GND 54 17 MDIO GND 53 18 MDC **Toward Bezel** GND 52 19 PRTAD4 RX LANE3-51 20 PRTAD3 RX LANE3+ 50 21 PRTAD2 GND 49 22 PRTAD1 RX LANE2-48 23 PRTAD0

VEND SPECIFIC

APS SET

RESERVED

APS SENSE

APS

3.3V

3.3V

5.0V

GND

GND

GND

24

25

26

27

28

29

30

31

32

33

34

35

Fig 18. 10Gb Host Board Pad Layout and Names

Lower Row Upper Row

RX LANE2+

RX LANE1-

RX LANE1+

RX LANE0-

RX LANE0+

RESERVED

RESERVED

GND

GND

GND

GND

GND [

47

46

45

44

43

42

41

40

39

38

37

36

Note: Refer to Fig 7 and Fig 8

#### 10.8 Management Interface

XENPAK transceivers support the MDIO interface specified in IEEE802.3ae Clause 45. In addition to the appropriate registers to support the IEEE standard there are some registers specific to XENPAK.

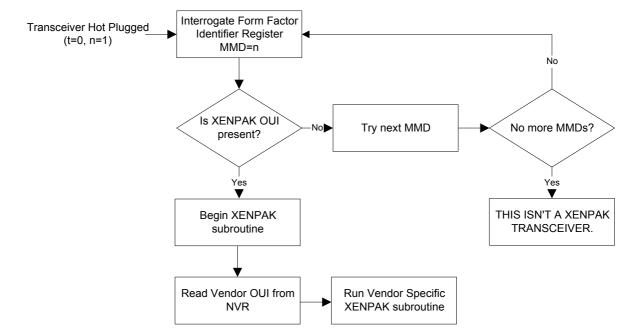

#### 10.8.1 Transceiver Identification

Efficient use of XENPAK and its specific registers requires an end-user system to recognize a connected transceiver as being of the XENPAK type. The method described in section 10.8.2. utilizes the Organizationally Unique Identifier (OUI) as a means of identifying it as a XENPAK and also of communicating the device in which the XENPAK specific registers are located. The XENPAK OUI is 00-08-BE,

For more info on OUIs see http://standards.ieee.org/regauth/oui/index.shtml

#### 10.8.2 OUI Method

Following successful hot plugging of a XENPAK transceiver it indicates its presence by pulling module detect low and shows that it is a XENPAK transceiver by placing a XENPAK specific OUI into the

Package Identifier registers at locations D.14 and D.15, as defined in 802.3ae clauses 45.2.1.10 and 45.2.3.8. D may be device 1, 2, 3, 4, 30 or 31.

The system performs a simple search for the XENPAK OUI across devices 1, 2, 3, 4, 30 or 31. Upon finding the XENPAK OUI the system knows that the XENPAK registers reside in that device.. Once the XENPAK registers are located, and OUI indicating the transceiver manufacturer (called Vendor OUI) can be read from the XENPAK registers (see 10.12.15) and any vendor specific actions taken by software, if required.

Fig 19. shows diagrammatically how the XENPAK OUI and Vendor OUI are used. Section 10.12.14. shows the format of the XENPAK OUI and its relation to the Package Identifier registers.

Fig 19. Transceiver Identification after Hot Plugging

#### 10.8.3 XENPAK Register Set

In addition to the standards related registers mandated by the IEEE in 802.3ae for each device, the XENPAK module shall maintain certain information in a set of non-volatile registers (NVRs) which can be read in the normal way via the MDC/MDIO management port. This memory is protected from writes by the system and is intended to be programmed at module manufacture.

The information defined for the NVRs may be required to use the module and shall have the location and format described in Table 1. Examples of information contained in the NVR include the indication of transceiver capabilities, manufacturer ID, and version number.

It should be noted that the NV Register set only uses the 8 least significant bits of the 16 bit MDIO register for data. Unlike 802.3ae registers which tend to use all 16 bits.

There is also an area of non-volatile memory in a XENPAK that can be read and written by the system.

Reads from this area are generally performed using standards MDIO reads from the specific address.

Writes to the customer area are volatile unless performed using the NVR Control/Status register, see Section 10.9 for more detail. A detailed layout of the NVR is given in Table 1 and details of it use given in 10.12.21 and 10.9

The exact implementation detail of the NVRs is beyond the scope of the MSA.

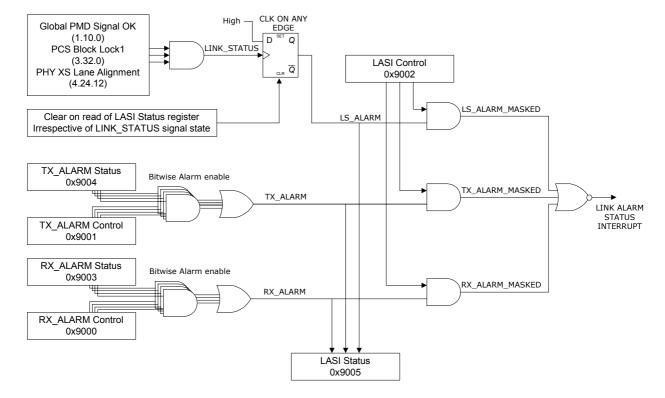

The high level layout of the XENPAK specific register areas is given in Table 13

A more detailed layout of the XENPAK non-volatile register use is given in Table 1

Table 13 XENPAK Register Set Overview

| ٠          | # D. +   | Avon Hongo                                       |

|------------|----------|--------------------------------------------------|

| Address    | # Bytes  | Area Usage                                       |

| 0x8000     |          | NVR Control/Status                               |

| 0x8001     |          | Vendor Specific                                  |

| to         |          |                                                  |

| 0x8006     |          |                                                  |

| 0x8007     | 2055     | Non-Volatile Registers                           |

| to         |          | Non Volume registers                             |

| 0x8106     |          |                                                  |

| 0x8107     | 1        | Extended Vendor Specific Non Volatile area       |

| to         |          | Extended vendor specific Norr volutile died      |

| 0x8806     |          |                                                  |

| 0x8807     |          | Reserved                                         |

| to         | 2041     | Nosci ved                                        |

| 0x8FFF     | 2011     |                                                  |

| 0.0111     |          |                                                  |

| 0x9000     |          | LASI Control & Status                            |

| to         |          |                                                  |

| 0x9005     |          |                                                  |

| 0x9006     |          | Reserved                                         |

| to         |          |                                                  |

| 0x9FFF     |          |                                                  |

| 0xA000     | 256      | Digital Optical Monitoring Functions             |

| to         | 230      | Digital Optical Monitoring Functions             |

| 0xA0FF     |          |                                                  |

| 0xA100     | 7        | Digital Optical Monitoring Control and Status    |

| to         | <b>'</b> | Digital Optical Fibrilitoring Control and Status |

| 0xA106     |          |                                                  |

| 0xA107     | 3833     | Reserved                                         |

| to         | 3033     | Noodived                                         |

| 0xAFFF     |          |                                                  |

| 07.0.11.11 | 1        | 1                                                |

| 0xB000     | 128      | LSS Registers - Optional                         |

| to         |          |                                                  |

| 0xB07F     |          |                                                  |

| 0xB080     | 1920     | Reserved                                         |

| to         |          |                                                  |

| 0xB07FF    |          |                                                  |

| 0xB800     | 16       | 10 GFC Registers - Optional                      |

| to         |          |                                                  |

| 0xB80F     |          |                                                  |

|            |          |                                                  |

| 0xB810     | 2032     | Reserved                                         |

|            | 2032     | Reserved                                         |

Table 14 NVR Register Map

| Field Group      | Register<br>Decimal | Register Address<br>Decimal Hex | NVR<br>Byte No. | Size         | e Name           | Description                             |          | Value                   | 7             | 9             | 2        | 4        | 3 2      | -        | 0        | Нех        |

|------------------|---------------------|---------------------------------|-----------------|--------------|------------------|-----------------------------------------|----------|-------------------------|---------------|---------------|----------|----------|----------|----------|----------|------------|

|                  | 32775               | 8007                            | 0               | 1            | Version          | XENPAK M SA Version supported           | rted     |                         | ×             | ×             | ×        | ×        | ×        | ×        | ×        | ×          |

|                  | 32776               | 8008                            | 1               | 2            | NVR_Size         | NVR Size in bytes                       |          |                         | ×             | ×             | ×        | ×        | ×<br>×   | ×        | ×        | ×          |

|                  | 32778               | 800A                            | 3               | 2            | Mem_Used         | Number of bytes used                    |          |                         | ×             | ×             | ×        | ×        | ×        | ×        | ×        | ×          |

| 1<br>0<br>0<br>0 | 32780               | 800C                            | 5               | 1            | Basic Addr       | Basic Field Address                     |          |                         | ×             | ×             | ×        | ×        | ×<br>×   | ×        | ×        | ×          |

|                  | 32781               | 800D                            | 9               | 1            | Cust Addr        | Customer Field Address                  |          |                         | ×             | ×             | ×        | ×        | ×        | ×        | ×        | ×          |

|                  | 32782               | 800E                            | 7               | -            | Vend Addr        | Vendor Field Address                    |          |                         | ×             | ×             | ×        | ×        | ×<br>×   | ×        | ×        | ×          |

|                  | 32783               | 800F                            | 8               | 2            | Ext Vend Addr    | Extended Vendor Field Address           | SSE      |                         | ×             | ×             | ×        | ×        | ×        | ×        | ×        | ×          |

|                  | 32785               | 8011                            | 10              | 1            | Reserved         |                                         |          |                         | ×             | ×             | ×        | ×        | ×        | ×        | ×        | ×          |

|                  | 32786               | 80.10                           | £               |              | Tovr Two         | Transcraiver tune                       |          | Unspecified             | 0             | 0             | $\vdash$ | $\vdash$ | $\vdash$ | $\vdash$ | 0        | 0          |

|                  | 25/00               | 200                             | =               | -            | )<br>  NO        | ומופספועם ואספ                          |          | XENPAK                  | 0 ;           | 0 ;           | $\dashv$ | +        | $\dashv$ | +        | $\dashv$ | -          |

|                  |                     |                                 |                 | $\downarrow$ |                  |                                         |          | Keserved                | ×             | × c           | × c      | ×        | ×        | ×        | × c      | × c        |

|                  |                     |                                 |                 |              |                  |                                         |          | palloadello<br>Co       | , c           | ) c           | +        | +        | +        | +        | +        | ·          |

|                  |                     |                                 |                 |              |                  |                                         | <u> </u> | 3 9                     | 0             | 0             | +        | +        | +        | +        | - 0      | - 2        |

|                  | 1                   | 9                               | ç               | ,            |                  |                                         |          | MT-RJ                   | 0             | 0             | 0        | 0        | 0        | 0        | 0        | 4          |

|                  | 32787               | 8013                            | প্র             | ~            | Connector        | Optical connector type                  | <u> </u> | ΩW                      | 0             | 0             | 0        | 0        | 0        | 0        | 0        | ∞          |

|                  |                     |                                 |                 |              |                  |                                         |          | FC/PC                   | 0             | 0             | 0        |          | 0        | 0        | 0        | ę          |

|                  |                     |                                 |                 |              |                  |                                         |          | Pigtail                 | 0             | 0             | -        | 0        | 0 0      | 0        | 0        | 20         |

|                  |                     |                                 |                 |              |                  |                                         |          | Reserved                | ×             | ×             | ×        | ×        | ×        | ×        | ×        | ×          |

|                  |                     |                                 |                 |              |                  |                                         |          | Unspecified             | 0             | 0             |          | Н        |          |          | 0        | 0          |

|                  | 32788               | 80 74                           | 5               |              | Encodina         | Bit encoding                            |          | NRZ                     | 0             | 0             | +        | -        | -        | 0        | _        | _          |

|                  |                     |                                 | !               |              | D<br>i<br>i      |                                         |          | FEC                     | 0 ;           | 0 ;           | +        | +        | $\dashv$ | +        | +        | 7          |

|                  |                     |                                 |                 | ļ            |                  |                                         |          | reserved<br>Incoppition | < <           | κ (           | +        | +        | +        | +        | +        | <b>₹</b> < |

| Basic            | 32789               | 8015                            | 4               | 7            | Bit Rate         | Nominal Bit Rate in multiples of 1M b/s | IMb/s    | o isbacillad<br>×       | ×             | > ×           | > ×      | > ×      | > ×      | > ×      | ×        | ×          |

| 2                |                     |                                 |                 |              |                  |                                         |          | Unspecified             | 0             | 0             | ╁        | ╀        | ╁        | ╀        | ┿        | 0          |

|                  |                     |                                 |                 |              |                  |                                         |          | 10GbE                   | 0             | 0             | 0        | 0        | 0        | 0        | _        | <u> </u>   |